메뉴열기

메뉴열기

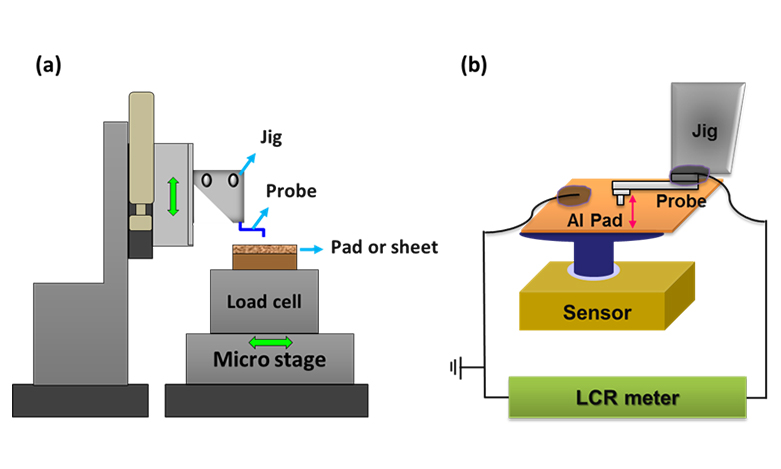

그림 1. (a) 접촉 실험 장치 개략도 (b) 전기 접촉 저항 측정 방법 개략도

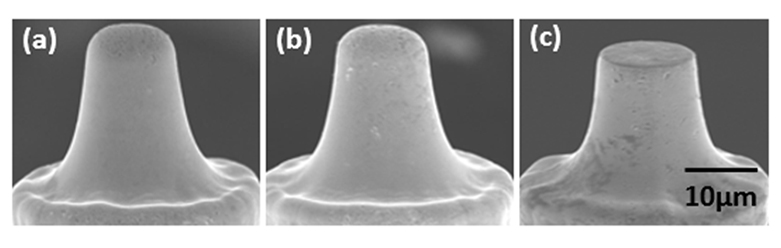

그림 2. SEM으로 측정한 프로브 팁 마모 형상 이미지(a) 초기 형상 (b) 알루미늄 패드와 500회 접촉 후 형상 (c) 클리닝 패드와 500회 접촉 후 형상

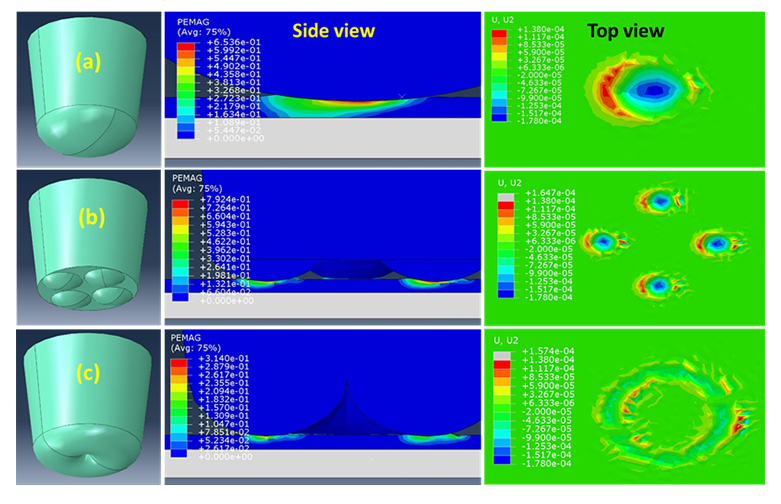

그림 3. FEM 시뮬레이션 결과 (a) 기존 구형 모양 팁 (b) 4-bump 팁 (c) 도넛 모양 팁