IJPEM

Engineering Surface Properties and Structural Designs for Controlling Underfill Dynamics in Flip-Chip Packaging

AI 반도체용 플립칩 공정의 핵심, 언더필 흐름 메커니즘 규명

김해진/연세대학교

- Flip-chip 패키징에서 발생하는 언더필 void와 불완전 충전 문제를 해결하기 위해, 기판 표면특성·bump 구조·언더필 조성의 상호작용을 체계적으로 규명.

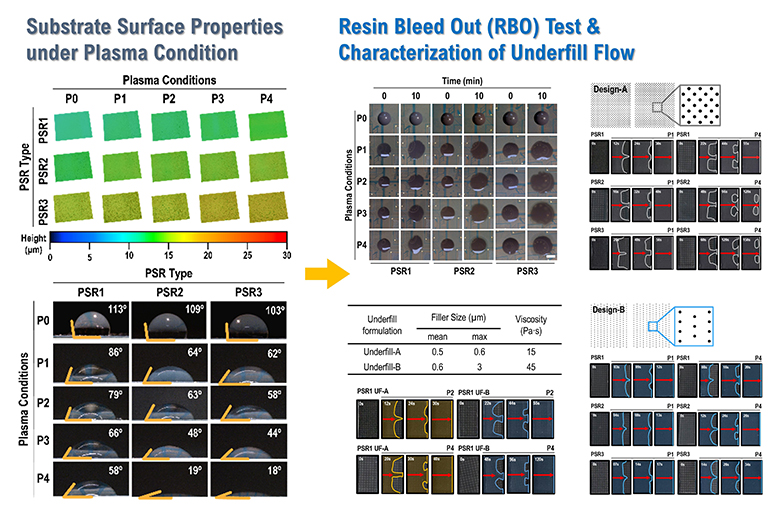

- 플라즈마 처리 강도에 따른 PSR(Photo Solder Resist) 표면 거칠기·접촉각 변화를 정량 분석하여, 표면 에너지 증대가 언더필 젖음성 향상과 Resin-Bleed-Out(RBO) 발생 간의 균형에 미치는 영향 규명

- Bump 배열 밀도 및 언더필 점도·필러 크기에 따른 유동 저항·void 형성 경향을 시각화하며, 저점도·미세필러 조성이 빠르고 균일한 충전 특성을 보임 확인.

- 기판 표면처리, 언더필 물성, Bump 설계가 언더필 유동에 미치는 상관관계를 규명함으로써, 차세대 AI 반도체용 고신뢰 패키징 공정의 기반 설계 지침 제시.

메뉴열기

메뉴열기